CIRCUITOS INTEGRADOS DIGITALES

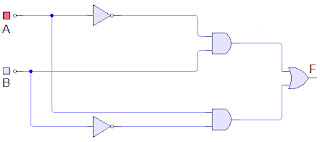

Circuitos digitales que contienen

compuertas lógicas

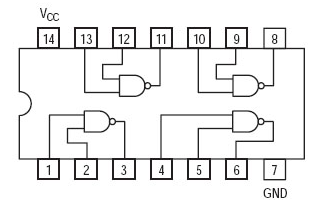

Los circuitos digitales que contienen

solamente compuertas lógicas se encuentran encapsulados con una estructura

DIL(dupl in line) de 14 pines preservándose los terminales 7 y 14 para la

alimentación(tierra y +vcc respectivamente).

Ejemplo de un circuito integrado de

compuertas nand:

Dado que existen compuertas de mas de

2 entradas resulta evidente que cuanto mayor sea la cantidad de entrada menor

será la cantidad de compuertas incluidas.

ESCALA DE INTEGRACION

A lo largo del tiempo los fabricantes

de componentes electrónicos han logrado aumentar la cantidad de componentes

construidos por unidad de superficie de los circuitos integrados, esto se

conoce como un aumento de la escala de integración.

Las ventajas de aumentar la escala de

integración son muchas, siendo las más importantes:

·

Permitir

la construcción de circuitos cada vez mas complejos.

·

Disminuir

el tamaño de los circuitos.

·

Disminuir

el consumo eléctrico

·

Hacer

circuitos mas confiables

·

Ser

más fáciles de cambiar

·

Bajar

los costos

Las escalas de integración fueron

aumentando a medida que mejoro la tecnología.

SSI (small scale integration)

En esta escala se producen circuitos

integrados que contienen funciones lógicas elementales como compuertas e

inversores, son aproximadamente 100 componentes.

MSI (médium scale integration)

Comprende

circuitos de aplicación general mas complejos como multiplexores, codificadores,

etc, con entre 100 y 1000 componentes.

LSI (large scale integration)

Gracias

a esta escala de integración se pudieron lograr circuitos electrónicos muy

complejos como memorias y micropocesadores entre 100 y 100000 componentes

VLSI

(very large scale integration)

Se alcanzo

esta tecnología en los años 80 lográndose circuitos integrados con más de 10

millones de componentes.

Actualmente

los microprocesadores que trabajan en la arquitectura de 64 bits y con una

frecuencia de 3 giga Hertz como es el caso de la serie entel, corel 7 , posee

alrededor de 700 millones de transistores.

CARACTERISTICAS GENERALES DE LAS COMPUERTAS

INTEGRADAS:

Las tecnologías

más conocidas en la fabricación de compuertas entegradas son la TTL y la CMOS ; y en ambas familias se

indica en las hojas de datos las siguientes características principales:

·

Tensión de alimentación y su tolerancia.

·

Temperatura de trabajo

·

Fan out (abanico de salida, cuantas puertas se

pueden colgar de cada una de las salidas de la compuerta)

VIL:

máxima tensión de entrada para un nivel bajo (0)

VIH:

Minima tensión de entrada para un nivel

alto (1)

VOL:

maxima tensión de salida para un nivel bajo (0)

VOH:

minima tensión de salida para un nivel alto (1)

§

Margen de ruido.

Indica

las variaciones máximas que se pueden producir a la entrada sin que la salida varíe

su estado.

§

Tiempo de propagación medio:

Es el tiempo que transcurre desde que se produce un cambio

lógico a la entrada hasta que lo hace a la salida (ns).

§

Disipación de potencia :

Normalmente se indica la disipación de potencia por función

.tamben se indican los consumos de corriente de alimentación y de entrada y salida

para los valores lógicos.

Cada una de las familias lógicas tiene su ventaja y su

desventaja, por ese motivo en cada caso se elegirá la más adecuada al diseño

que se vaya a desarrollar.

Las características ideales de una familia lógica ideada son

las siguientes:

§

Alto grado de integración

§

Alta velocidad de propagación

§

Mínimo consumo

§

Máxima inmunidad al ruido y a las variaciones de

temperatura

§

Compatibilidad con otras familias lógicas

§

Bajo costo.

FAMILIA TTL

(transistor-transistor logic)

Surgió

como el ultimo desarrollo para crear funciones lógicas mediante semiconductores

.Anteriormente se habían desarrollado las familias Dl (lógica de diodos). RTL

(lógica resistor transistor), HTL(lógica de alto umbral), ECL(lógica de acoplamiento

por emisor)

En esta

familia lógica las compuertas están construidas mediante resistores, diodos y

transistores bipolares, por lo que esta familia posee las características

generales de estos últimos. Con esta

tecnología se fabrican además de compuertas otros circuitos de mayor complejidad

en escala MSI (codificadores, multiplexores, etc.)

La

familia TTl comprende varias series, que han sido desarrolladas a partir de la

serie estándar, para mejorar algunas de las características de las fabricadas

anteriormente.

La primera

serie es decir la estándar se conoce como serie 74.Cuyas características son

las siguientes:

·

Tensión de alimentación : 5v +- 10 %

·

Temperatura de trabajo : 0ºC a 70ºC

·

Fan-out : 10

Niveles

de tensión:

VIL=0,8V

VJH: 2V

VOL: 0.4v

VOH: 2.4v

Valores

de ruidos en ambos niveles: 0.4V

Tiempo

de propagación medio: 10ns

Disipaciond

e potencia :10 mW por función.

La

serie 54, presenta las mismas características que la 74, pero se desarrollo

inicialmente para aplicaciones militares y aeroespaciales y se diferencia

fundamentalmente en que su temperatura de trabajo esta comprendida entre -56 °C a + 125°C

Con el

fin de mejorar los tiempos de conmutación, y/o la disipación de potencia se han

desarrollado las siguientes series 74/54 L (low power).

En esta

serie se obtiene menor consumo 1mW por función pero el tiempo de propagación es

de 33 ns.

74/54

S (shottky)

Incorpora diodos Shottky para

llevar el tiempo de propagación a 3 ns.

74/54

LS ( Low power shottky)

Combina las ventajas de las series anteriores con una

potencia disipada por compuerta de 2mW y un tiempo de propagación de 10nS.

74/54 ALS(advanced low power

schottky)

Potencia de disipación por

compuerta de 1 m

watt y un tiempo de propagación de 4ns.

74/54

AS ( advanced shottky )

Esta serie se desarrollo para

aplicaciones con bajo tiempo de propagación, llegando a 1.5ns con una

disipación de potencia de 7mw.

En los circuitos integrados más

complejos formados por muchas compuertas, las potencias disipadas y los tiempos

de propagación son mayores ya que se van acumulando los de las funciones

básicas que las componen.

FAMILIA C MOS ( complemental metal oxide semiconductor)

Su nombre se debe a la

utilización de un componente denominado transistor MOS. Se llaman

complementario por que se utilizan transistores de canal P y de canal N en

forma complementaria, a decir: transistores NMOS y PMOS.

Estos circuitos integrados se

comenzaron a desarrollar posteriormente a los de la familia TTL y presentan

ventajas y desventajas respecto a ella. La principal ventaja es la menor

disipación por función, lo que permite una mayor integración, y su principal

desventaja es su tiempo de propagación.

La familia CMOS básica es la

denominada serie 4000 y en ellas se incluyen dispositivos complejos como contadores,

registros, memorias, microprocesadores y microcontroladores.

Serie estándar (4000)

Alimentacion eléctrica : 3 a 8 V

Fan out: superior a 50

Temperatura de funcionamiento: -40°C a 85°C

Niveles de tensión para una

tensión de alimentación de 5 V:

VIL=1.5 v

VIH=3.5v

VOL=0.05v

VOH=4.95v

Inmunidad al ruido:

No le afectan cambios de hasta

un 30 % de la tensión de alimentación, los tiempos de propagación son

inversamente proporcional a la tensión de alimentación , siendo de 50nSpara 5v

y 30nS para 10v.

La potencia disipada por cada

función es del orden de los 10nW.

Las familias que se

desarrollaron posteriormente son las siguientes:

54/74 HC ( high speed Cmos)

Se mejora el tiempo de propagación

llegando a valores de 8ns con tensiones de alimentación comprendidas entre 3 y

6v.

54/74 HCT ( high speed Cmos comp

TTL)

Tiene las características del

HC y es eléctricamente compatible con la TTL. (Alimentación 5v)

Las series mas modernas de CMOS

son las 54/74 AC y 54/74 ACT

En el primer caso la tensión de

alimentación esta entre 3v y 6v compatible con la HC.

En el segundo caso se alimenta

con 5v por lo que puede sustituir a la serie 54/74 HCT y a toda la familia TTL.

Potencia por función 1mW, tiempo de propagación 3nS.