CIRCUITOS SECUENCIALES

1) Para el siguiente circuito

verificar su funcionamiento como fllip-flop encontrando las condiciones de set,

reset, almacenamiento y condición prohibida. Realizar además una tabla que

resuma su funcionamiento.

2) Idem anterior para el siguiente circuito.

3) Construir un flip-flop RS sincronico utilizando 4 compuertas nand y basandose en el circuito del ejercicio Nº1 confexionar su tabla de funcionamiento.

4) ¿Para que se utiliza el clock en los circuitos digitales?. Indique sus parámetros principales.

Una señal de

reloj (en inglés clock signal, o simplemente clock) es en la electrónica digital una señal binaria,

que sirve para coordinar las acciones de varios circuitos,

en especial para la sincronización de biestables en sistemas digitales complejos. Según

su aplicación, la señal de reloj se puede repetir con una frecuencia

predefinida o también ser aperiódica.

En los casos en

los que hay una señal de reloj, suele darse por medio de un generador de reloj. La

señal oscila entre un

estatus alto y bajo, que se caracteriza por un período de oscilación o bien por un valor de cambio, la

frecuencia de reloj y el ciclo de trabajo.

Los circuitos que utilizan la señal de reloj para

sincronizarse, pueden, según su construcción, basarse en el flanco ascendente o en el descendente de la

señal (en el caso de DDR se utilizan

ambos flancos).

En hojas técnicas

y diagramas a la señal de reloj se le suele describir como CLK.

La mayoría de

circuitos integrados complejos requieren una señal de reloj, para sincronizar

diferentes partes del chip y equilibrar los retrasos de las puertas. Dado que los chips son cada vez más complejos, es

cada vez más difícil proveer de una señal de reloj precisa y homogénea en todos

los sitios. Ejemplo ilustrativo de este problema son los microprocesadores, componente central de losordenadores modernos. Para los transistores se

suele indicar la frecuencia, hasta la que es posible amplificar una pequeña

señal. Ésta suele ser diez veces mayor a la frecuencia de reloj.

5) Los siguientes trenes de pulsos se encuentran aplicados al flip-flop RS sincronico del ejercicio Nº3. Dibujar los trenes de pulsos correspondientes a las salidas Q y no Q.

6) Construir un circuito practico de flip-flop RS sincronico utilizando un circuito integrado 7400.

7) Dibujar el bloque de un flip-flop JK y su tabla de funcionamiento.

8) Los siguientes trenes de pulsos se encuentran aplicados al flip-flop JK. Dibujar las salidas Q y no Q.

9) Los siguientes trenes de pulsos se encuentran aplicados a un flip - flop RS sincronico y a un JK sincronico. Dibujar las salidas Q y no Q para cada uno de ellos. Condicion inicial reset.

10) Los siguientes trenes de pulsos se encuantran aplicados a un flip - flop JKMS construido con 2 flip - flop JK y un invensor. Dibujar los trenes de pulsos a la salida de cada flip - flop y verificar que el circuito se comporto como un flip - flop disparado por flanco descendete.

11) Los siguientes trenes de pulsos se encuantran aplicados a un flip - flop JKMS disparado por flanco desdente como el ejercicio anterior. Dibujar las salidas Q y no Q finales. El flip - flop se halla inicialmente en condicion de reset.

j 12: Desarrollar un contador asincrónico que cuente de forma ascendente de 0 a 7 y vuelva a cero.

Ej13 Utilizando flip flops JKMS disparado por flanco descendente por la siguiente tabla de funcionamiento. Diseñar un contador asincrónico que cuente de 0 a 5.

Ej 14

Diseñar un contador asincrónico que cuente en forma descendente de 7 a 0.

Ej 15

Construir un circuito práctico que permita verificar el funcionamiento del CI 4024.

Ej 16

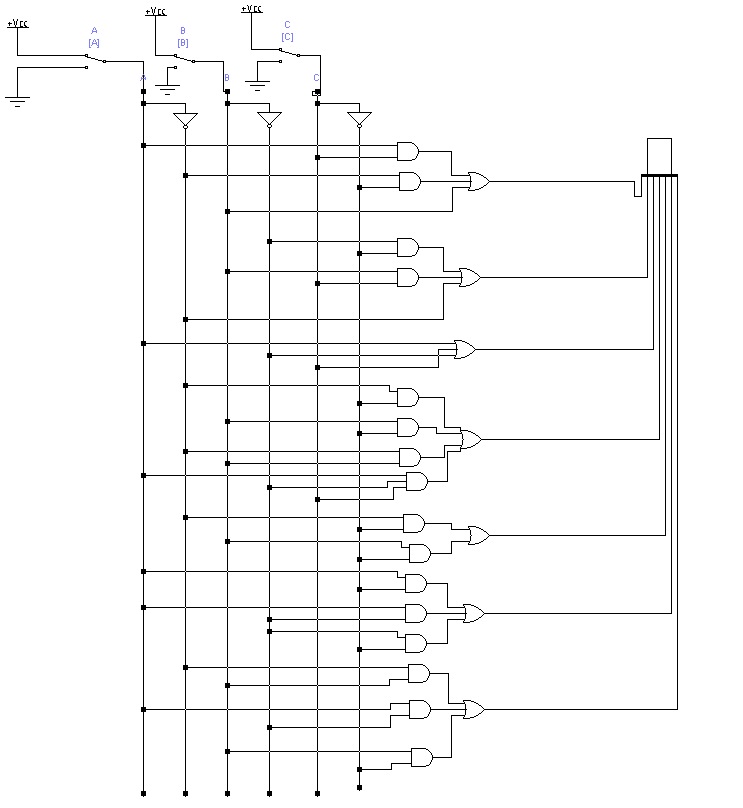

Desarrollar un contador sincrónico que cuente de forma ascendente de 0 a 7 y vuelva a cero.

Ej 17: Construir un circuito práctico que permita

verificar el funcionamiento del circuito integrado

74190. Copiar y pegar su hoja de datos. Explicar que

función cumple cada uno de sus pines de conexión.

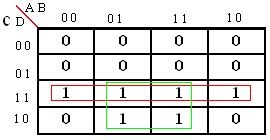

Ej 18: Utilizando FF desarrollar un circuito contador

sincrónico de 0 a 9 y vuelva a cero.

Ej 19: Construir un contador sincrónico que pase por

los siguientes estados 0, 1, 2, 4, 6, 0

Ej 20: Construir un registro de dezplazamiento de 4 bits con entradas serie y paralelo y salida serie y paralelo. Utilizar el Ci 7476, las compuertas que hagan falta y los indicadores necesarios para verificar su funcionamiento.

Ej 21: Construir un circuito que permita verificar el funcionamiento del Ci 74195.

.bmp)

.bmp)

.bmp)

.bmp)

.bmp)

.bmp)

.bmp)

.bmp)

.bmp)